Che cos’ è vtfet?

vtfet

Progressi significativi sono stati compiuti nella progettazione di semiconduttori grazie alla collaborazione tra IBM research, samsung e il nostro partner Albany research alliance. La nostra nuova strategia, denominata transistor a effetto fetale in nanofogli per il trasporto verticale (vtfet), potrebbe essere fondamentale per mantenere in vigore la legge di Moore nei prossimi anni.

Il vtfet rappresenta un’architettura rivoluzionaria del transistor. A differenza dei modelli tradizionali, questo transistor innovativo utilizza fogli nanometrici sottili per facilitare il flusso verticale della corrente elettrica, a differenza del flusso laterale tradizionale. Ciò comporta migliori prestazioni e una maggiore efficienza nel consumo di energia.

Un aspetto fondamentale del vtfet è la sua capacità di integrare un numero maggiore di transistor in un chip, senza che ciò implichi un aumento significativo delle sue dimensioni. Consentendo il flusso di corrente verticale, si riduce la distanza che il segnale elettrico deve percorrere, con conseguente ottimizzazione della velocità e dell’efficienza di trattamento.

Inoltre, il vtfet è più resistente alle perdite di calore ed elettricità, il che lo rende un’alternativa promettente per applicazioni che richiedono elevate prestazioni ed energia. Ciò è particolarmente importante in settori quali l’intelligenza artificiale e l’informatica quantistica, in cui è necessaria l’elaborazione rapida e intensiva di grandi volumi di informazioni.

L’approccio vtfet sviluppato da IBM research e samsung mostra come l’innovazione costante e l’esplorazione di nuovi approcci possano superare gli attuali limiti tecnologici. Anche se la legge di Moore sta forse raggiungendo il suo limite in termini di aumento del numero di transistor su un chip, questa tecnologia emergente indica un percorso promettente, e le cifre che tratterò in seguito la supportano.

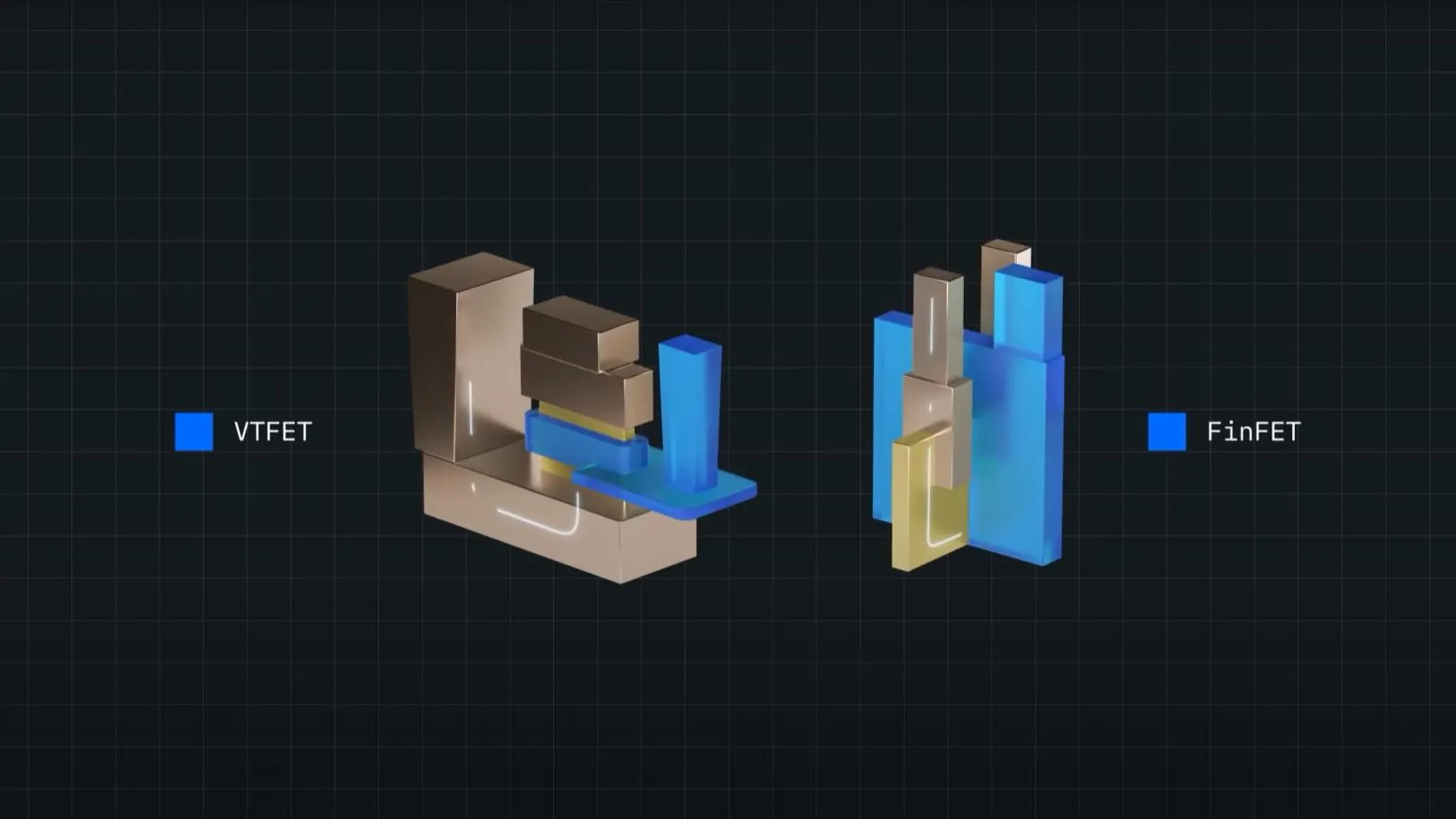

Attualmente, le nuove configurazioni predominanti del chip sono basate su transistor a effetto di campo di trasporto laterale, come il transistor a effetto di campo pinne, noto come finfet, a causa della sua somiglianza con la pinna posteriore di un pesce. Questi transistor sono impilati sulla superficie di un wafer di silicio.

Al contrario, il vtfet organizza i transistor perpendicolarmente al wafer di silicio e canalizza la corrente elettrica In direzione verticale verso la superficie del wafer. Questo nuovo approccio affronta gli ostacoli della scalatura allentando i vincoli fisici relativi alla lunghezza della porta del transistor, allo spessore dello spazio trai componenti e alle dimensioni dei contatti, in modo che ciascuna di queste proprietà possa essere ottimizzata in termini di rendimento o di efficienza energetica.

Tramite vtfet è stata dimostrata con successo la possibilità di sfruttare la scala al di là della tecnologia dei semiconduttori cmos odierni. In questi nodi avanzati, il vtfet potrebbe offrire fino a un doppio rendimento o una riduzione fino all’85 per cento del consumo energetico rispetto all’alternativa su scala ridotta del finfet. Infatti, l’ibm ha annunciato un chip wafer con trattamento a 2nm e 50 milioni di transistor In uno spazio simile a quello delle unghie.

Forse vorreste anche sapere quali sono i migliori microprocessori sul mercato

In passato, i progettisti aumentavano la densità dei transistor su un chip riducendo la larghezza e le interconnessioni dei cancelli. Lo spazio fisico in cui tutti i componenti sono disposti è denominato ‘gate pass connesso’ (CGP), ossia la distanza minima tra le porte dei transistor. La capacità di ridurre i passaggi di porta e di connessione ha permesso ai progettisti di circuiti integrati di passare da migliaia a milioni di transistor nei nostri dispositivi. Tuttavia, con le tecnologie più avanzate di finfet, c’è solo un po’ di spazio per spaziatori, porte e contatti. Una volta raggiunto il limite CGP, non rimane più spazio.

Dirigendo verticalmente il flusso di corrente elettrica, porte, distanziatori e contatti non sono più limitati dalle modalità tradizionali. In altre parole, c’è la possibilità di espandere la CGP mantenendo al contempo un transistor, un contatto e un isolamento adeguati (chiamato isolamento di fosse poco profonde o sti).

Liberandoci dai limiti della disposizione laterale e del flusso di corrente, i ricercatori sono stati anche in grado di utilizzare contatti più ampi fonte/scarico per aumentare la corrente nel dispositivo. La lunghezza della porta può essere regolata per ottimizzare la corrente conduttrice e la perdita del dispositivo, mentre lo spessore del distanziatore può essere regolato indipendentemente per ridurre la capacità.